### International Journal of Future Innovative Science and Engineering Research (IJFISER) Volume - 2, Issue - II ISSN (Online): 2454- 1966

# Transient Response Boosted D-LDO Regulator Using Starved Inverter Based VTC

#### K.K.Sree Janani, M.Balasubramani

P.G. Scholar, VLSI Design, Assistant professor,

Department of ECE,

Vivekanandha College of Engineering for Women, Namakkal, Tamil Nadu, India.

E-Mail: sreejananipriya@gmail.com, mskbalasubramani@gmail.com

JUNE - 2016

www.istpublications.com

## Transient Response Boosted D-LDO Regulator Using Starved Inverter Based VTC

#### K.K.Sree Janani, M.Balasubramani

P.G. Scholar, VLSI Design, Assistant professor,

Department of ECE,

Vivekanandha College of Engineering for Women, Namakkal, Tamil Nadu, India.

E-Mail: <a href="mailto:sreejananipriya@gmail.com">sreejananipriya@gmail.com</a>, mskbalasubramani@gmail.com

#### **ABSTRACT**

A Digital Low-Dropout Regulator (D-LDO) with reduced transient response time and with control of overshoot/undershoot is proposed. The response time is reduced by using transient response boost technique. To maintain the stable output the loop gain is increased at the time of deviations exceeding the limit and the loop gain is returned after the output voltage is settled to a predefined value. The LDO with transient response boost technique has less settling time than the LDO without transient response boost technique. The regulation is done in time mode with the help of high linear Voltage to Time Convertor (VTC) using starved inverters and time to digital convertor. The time domain analog to digital conversion achieves high resolution at low power and small area. And multibit vernier cyclic TDC for high level current efficiency is used.

**Key words**—Current efficiency, cyclic TDC, digital low-dropout regulator (D-LDO), starved inverters, transient-response boost mode (TRBM), voltage-to-time converter (VTC).

#### I. INTRODUCTION

Nowadays the battery powered devices plays an important role and various applications are embedded in a single device as seen in various SoCs. Here the power management unit is the major part since the power from battery is limited in capacity. Thus the on-chip LDO are gaining more attention as a power management unit. However, most of research works on the LDO voltage regulator still focus on the analog control. Compared to the design flow of the analog approach, the digital design flow presents the following difference: designers specify the size of power MOSFET, load requirement, output capacitor value, and its ESR value. In case of analog LDOs driving near threshold and sub-threshold logic circuits a difficulty is imposed in maintaining the low dropout voltage. The time domain ADC can provide higher resolution.

The simple structure of LDO composed of simple convertor consisting binary comparator and shift register. The transient response time is reduced by means of increasing the clock frequency [5] which can be achieved with the help of asynchronous shift register. Multibit ADC provide faster loop operation through direct measurement of voltage difference. TDC based 4-bit ADC with Proportional-Integral-Derivative (PID) controller provide stability compensation and fast transient response is achieved through dynamic clock scaling but it results in high quiescent current. The ADC without PID controller results in higher voltage ripples due to insufficient resolution. Thus power efficient digital linear LDO regulator based on multibit cyclic TDC for high level current efficiency is employed.

#### II. RELATED WORK

A digitally controlled low-dropout voltage regulator with fast transient response and auto-tuned voltage is achieved by means of an autotuning algorithm [3]. Test of the autotuning algorithm shows that the LDO is able to work at its optimal performance under various uncertain conditions and even when the supply voltage is going lower. Digital controller processes discrete signal and operate with logic gates. No matter what the scale of the supply voltage is, so long as the supply voltage ensures the normal operation of logic gates, there is no impact of the voltage level on the compensation design. Accordingly, the transfer function is derived for choosing appropriate type of the compensator. This design flow also allows designers to implement programmable features which are more suitable for customization. In charge balance algorithm [3], from frequency analysis point of view, the cross-over frequency is limited by the phase margin to ensure enough stability margins. However, confining the cross-over frequency to some range may slow down the transient response of the power converter. To speed up the transient response without increasing the cross-over frequency [5], a charge balance concept is used and it was successfully applied to dc—dc switching converter. Due to the different operation principles between the switching converter and the LDO regulator, the charge balance algorithm should be revised before applying to the LDO. Additionally using the

asynchronous shift register, instead of the typical synchronous shift registers is efficient. But, it still has a problem, in that circuit operation is too sensitive to PVT variation, to get constant performance between chips. A multibit ADC can provide faster loop operation through direct measurement of the voltage difference. Also, it allows for designers to implement the algorithms of more complex loop compensation and loop acceleration.

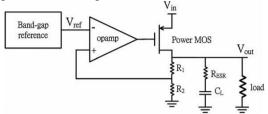

Fig. 1. Simple structure of LDO digital LDO with PLL

A Conventional D-LDO regulator adopting the synchronous control scheme in which the operation is realized using clock signal. The comparator is used to compare the output voltage with the reference voltage and the power switches are activated using the shift registers. When large output power is requested to the D-LDO regulator, the comparator would detect the occurrence of insufficient energy at the so that more power switches are turned on to provide the supplementary current. Operating clock frequency is the main parameter affecting the performance of the synchronous D-LDO regulator.

Due to the infinite bandwidth of the comparator, the shift register can be immediately informed to either increase or decrease the driving capability of power switches when the output loading is changed. Shift registers determined the transient speed because the shift register allows only one power switch to be turned on or off within per clock cycle in the synchronous D-LDO regulator. If the synchronous D-LDO regulator operates with a slow frequency clock, small power consumption realizes the better current efficiency, compared with current efficiency which is derived with the fast frequency clock [4]. This result in larger current dissipation and due to the usage of slow clock frequency speed is affected. However, fast tracking speed can be achieved by adopting the high frequency clock in a synchronous D-LDO regulator but results in the worse current efficiency compared with that when operating with a slow frequency clock. That is, higher frequency operation leads to faster voltage tracking speed. Moreover, the current efficiency of the D-LDO regulator is inversely proportional to the frequency of the clock signal.

Fast voltage tracking speed can be ensured; however, current efficiency will be deteriorated in the synchronous D-LDO regulator with a high frequency clock. A trade-off between voltage tracking speed and current efficiency exists in the clock-triggered synchronous D-LDO regulator design.

#### III. PROPOSED SYSTEM

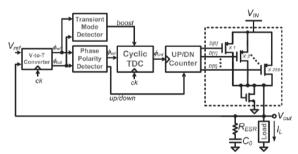

In this paper, a new scheme of power-efficient digital linear LDO regulator based on a multibit cyclic TDC is proposed for high-level current efficiency, while targeting on driving super-to-near-threshold logic gates [6]. The highly linear VTC circuit is used employing basic current starved inverters. To compensate for the degraded transient performance, we propose a transient response boost technique [1], which detects undershoot/overshoot during transient response, and creates additional asynchronous clocks only during that time. The loop gain is increased to settle down the deviated output voltage. The various blocks employed in the proposed digital LDO regulator are presented in the below sections.

Fig. 2 .Block diagram of digital LDO regulator

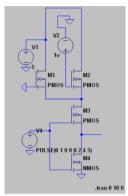

#### A. Voltage to time converter

Time-based ADC is an essential block in designing software radio receivers because it exhibits higher speed and lower power compared to the conventional ADC, especially, at scaled CMOS technologies. In time-based ADCs, the input voltage is first converted to a pulse delay time by using a Voltage-to-Time Converter (VTC) circuit [2], and then the pulse delay time is converted to a digital word by using a Time-to-Digital Converter (TDC) circuit. The VTC achieves high linearity and large dynamic analog input range. A new VTC circuit, based on the current starved inverter architecture, is proposed. The proposed circuit exhibits higher linearity and low power consumption compared to the previously published

VTC circuits. The architecture of the proposed VTC circuit [2] is based on the PWM method and achieves high insensitivity to process and temperature variations. a basic current starved differential delay cell with the addition of weak cross coupled inverters to reduce the transition times of the inverters used. A similar VTC is presented in [9] but a weak nMOS transistor with its gate tied to the supply voltage is added to ensure that the VTC operates at very low input voltages.

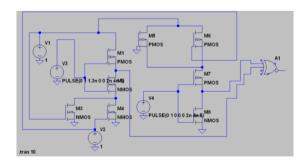

Fig. 3. trise current starved inverter circuit

A delay unit consisting of a series of inverters with the Pmos sources tied to the input voltage is introduced The previous VTC circuits are not sufficiently linear and their voltage to time conversion sensitivity is not high enough to be used in high speed, low power, and high resolution time-based ADCs.

Fig. 4. tfall current starved inverter circuit

The input clock, VCLK, is applied to the tFALL current starved circuit and accordingly, the voltage V1 is an inverted version of the clock where only the falling delay is controlled by the input voltage. On the other hand, the input clock is applied to an inverted delay line (i.e., odd number of CMOS inverters) and then applied to the tRISE current starved circuit. Accordingly, the voltage V2 is a delayed version of the input clock where the rising delay is controlled by input voltage.

Fig. 5. Block diagram of VTC

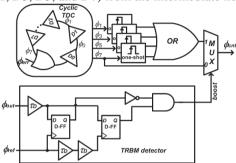

#### B. Transient-Response Boost Mode (TRBM) Operation

When the load current jumps up from a steady-state condition, Output voltage is instantly dropped, since the current is drawn from load capacitor, which is much faster than adjusting the gate of the power transistor, through the loop response operating at clock frequency. The D-LDO takes over the loop control [1], to correct output voltage after the delay of  $\tau f$ , inversely proportional to the closed loop bandwidth. With this property, we need to increase the bandwidth to reduce  $\tau f$ , and to reduce the peak undershoot at the same time. This goal can be achieved by increasing the overall size of the pMOS transistors, assuming that all the other loop conditions are kept unchanged. However, it causes the voltage ripple to increase, which is unavoidable in such D-LDO regulators. To solve this tradeoff issue, we employed a gain-boosting technique activated only for the transient period, which is named the transient-response boost mode (TRBM). The TRBM detector

monitors the magnitude of the undershoot/overshoot, then it controls our D-LDO to increase the loop gain as needed, if Output voltage goes beyond a predetermined boundary condition. Once Output voltage is reduced to within the boundary values, the loop gain returns to smaller normal value.

The TRBM detector triggers the output (boost) HIGH, when the time difference between  $\varphi$ ref and  $\varphi$ out is increased beyond  $\tau D$  or more, which means that Vout deviates from a preset boundary, because of the overshoot/undershoot during the transient response.

In cyclic TDC, sharing the delay cells for resolution of each bit in this way results in good linearity, as well as the basic advantage of the power and area efficient design, since the mismatch between delay cells is repeated equally for each bit. Also, it provides a wide dynamic range, because the dynamic range is limited by the number of bits in the UP/DN counter, not by the total delay range of TDC. Once TRBM is entered, the number of pulses in  $\varphi$ cnt is multiplied four times, by tapping the non-overlapped clocks (D1, D3, D5, and D7) from the intermediate nodes of the delay chain.

Fig. 6. TRBM detector with cyclic TDC

This leads to effectively increasing the loop gain by four times, and thus accelerating the loop operation. With this scheme, we can reduce the overshoot/undershoot on Vout, without any detrimental effect on the ripple after the loop settles down. It should be noted that this performance is achieved by just an UP/DN counter, not by more complex adders and multipliers.

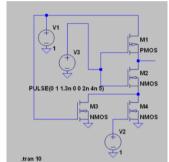

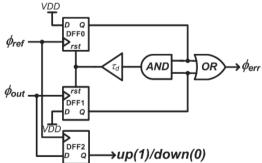

#### C. Phase and polarity detector

A three-state phase-frequency detector (PFD) with polarity detector is as shown below. The PFD is composed of two D flipflops with asynchronous reset, AND, and OR gates. If  $\phi$ ref goes to HIGH, while all the D flip-flops keep LOW, Q of DFF0 is raised to HIGH. If this event is followed by a rising transition on  $\phi$ out, Q of DFF1 goes to HIGH as well, then the AND gate resets both the flip-flops (DFF0 and DFF1) to LOW after the buffer delay of  $\tau d$ , an intentionally made delay, to remove the dead-zone problem in the cyclic TDC. The polarity detector is implemented with a single D flip-flop (DFF2). This circuit discerns the first-coming clock between  $\phi$ ref and  $\phi$ out, which represents that the corresponding voltage is lower than the other. As an example, if  $\phi$ ref is faster than  $\phi$ out, i.e., Reference voltage lower than Output voltage, the output of up/down is set to LOW, so that the counter is decremented. The TRBM detector triggers the output (boost) HIGH, when the time difference between  $\phi$ ref and  $\phi$ out is increased beyond  $\tau$ D or more, which means that Output voltage deviates from a preset boundary, because of the overshoot/undershoot during the transient response.

Fig. 7. Phase and Polarity Detector Circuit

The TRBM detector triggers the output (boost) HIGH, when the time difference between  $\varphi$ ref and  $\varphi$ out is increased beyond  $\tau D$  or more, which means that Vout deviates from a preset boundary, because of the overshoot/undershoot during the transient response. Once TRBM is entered, the number of pulses in  $\varphi$ cnt is multiplied four times, by tapping the nonoverlapped clocks (D1, D3, D5, and D7) from the intermediate nodes of the delay chain. This leads to effectively increasing the loop gain by four times, and thus accelerating the loop operation. With this scheme, we can reduce the overshoot/undershoot on Vout, without any detrimental effect on the ripple after the loop settles down.

#### IV RESULT ANALYSIS

The fig.8 is output waveforms for the voltage signal in time mode converted using VTC. Both the feedback and the reference voltage are converted where the delay of the pulse corresponds to the voltage value.

Fig.8.Output waveform for VTC using starved inverter

#### **V CONCLUSION**

In this paper, a digital LDO regulator is proposed operated in time domain using a VTC which has high linearity and large dynamic analog input range. The regulator operates in the time domain to achieve higher resolution. The transient response boost technique is employed to reduce the transient response time without increasing the ripples. The loop gain is increased to maintain stable output voltage by transient response boost technique also improves the current efficiency.

#### REFERENCES

- [1] Tak-Jun Oh and In-Chul Hwang, "A 110-nm CMOS 0.7-V Input Transient-Enhanced Digital Low-Dropout Regulator With 99.98% Current Efficiency at 80-mA Load" IEEE transactions on Very Large Scale Integration (VLSI) systems, June 2015

- [2] Hassan Mostafa1 and Yehea I. Ismail, "Highly-Linear Voltage-to-Time Converter (VTC) Circuit for Time-Based Analog-to-Digital Converters (T-ADCs)", IEEE 20th International Conference on Electronics, Circuits, and Systems, Dec. 2013

- [3] Y.-C. Chu and L.-R. Chang-Chien, "Digitally controlled low-dropout regulator with fast-transient and autotuning algorithms," IEEE Trans. Power Electron., vol. 28, no. 9, pp. 4308–4317, Sep. 2013

- [4] Y.-H. Lee et al., "A low quiescent current asynchronous digital-LDO with PLL-modulated fast-DVS power management in 40 nm SoC for MIPS performance improvement," IEEE J. Solid-State Circuits, vol. 48, no. 4, pp. 1018–1033, Apr. 2013.

- [5] K. Otsuga et al., "An on-chip 250 mA 40 nm CMOS digital LDO using dynamic sampling clock frequency scaling with offset-free TDC based voltage sensor," in Proc. IEEE Int. SOC Conf. (SOCC), Sep. 2012.

- [6] W.-C. Hsieh and W. Hwang, "All digital linear voltage regulator for super-to near-threshold operation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 6, pp. 989–1001, Jun. 2012.

- [7] Y. Okuma et al., "0.5-V input digital LDO with 98.7% current efficiency and 2.7-μA quiescent current in 65 nm CMOS," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Sep. 2010.

- [8] A. Raychowdhury, D. Somasekhar, J. Tschanz, and V. De, "A fully digital phase-locked low dropout regulator in 32 nm CMOS," in Proc. IEEE Symp. VLSI Circuits, Jun. 2012.

- [9] P. Chen, C.-C. Chen, W.-F. Lu, and C.-C. Tsai, "A time-to-digital converter- based CMOS smart temperature sensor," IEEE J. Solid-State Circuits, vol. 40, no. 8, pp. 1642–1648, Aug. 2005.